Advanced RF Transceiver Meets the Demands of SDR Applications

- 2014-08-21 13:55:00

- admin

- 转贴:

- http://www.microwavejournal.com/articles/21285-advanced-rf-transceiver-meets-the-demands-of-sdr-applications

- 4224

The solution seems obvious: minimize use of dedicated hardware and instead rely on a software-defined radio (SDR) to implement and manage as much of the transmitting and receiving functionality as possible. Today’s high-performance, low-power processors, including FPGAs, and their ability to execute complicated algorithms at high speed make such real-time implementation practical.

But there is a real-world impediment to this solution: it is difficult to design wideband analog circuitry for the receiver and transmitter signal paths. As a result, most broadband SDRs use a set of overlapping, parallel analog channels, each optimized for a specific slice of the overall band, and with bandwidths matched to the signals of interest in each segment. While this approach is technically effective, it requires considerable hardware, PC board real estate, power and, of course, cost.

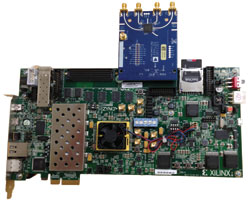

That’s the dilemma Epiq Solutions (Schaumburg, IL) faced as it developed its latest SDR unit, the MaveriqTM Multichannel Reconfigurable RF Transceiver (shown in Figure 1), an advanced platform combining multiple RF transceivers, an internal solid state drive (SSD) for data recording, an on-board Intel ×86 CPU running Linux, and a gigabit Ethernet interface for high-speed data access. It offers significant SDR capability in a small package and covers a tuning range from 100 MHz to 6 GHz. As designers and builders of state-of-the-art, reconfigurable radio systems for mission-critical applications, the company’s objective was to deliver a more powerful multi-channel version of its existing MatchstiqTM SDR.

Despite its advanced features and capabilities, Maveriq is a portable, low-power platform, while previous solutions required large and bulky hardware configurations. Combined with a library of ready-to-run specialty software applications, Maveriq can immediately be used to solve challenging signal-processing requirements. These include scanning and decoding cellular radio signals from both base stations and mobile phones; recording wideband RF to its internal hard drive (SSD) as well as RF playback; and implementing 2 × 2 multiple input, multiple output (MIMO) waveforms.

Enabling a New Design Approach

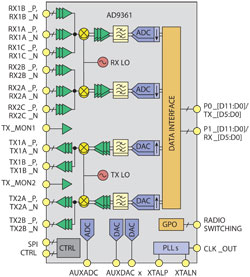

What allowed the engineers at Epiq to pack this much performance into a small, low-power unit was the availability of a new IC, the AD9361 RF Agile Transceiver from Analog Devices, specifically tailored for SDR applications. According to John Orlando, Epiq’s CEO and system architect, “The AD9361 provides the RF flexibility and integration needed to enable our next generation SDR platform.”

This 10 × 10 mm chip-scale device with dual independent channels, as shown in Figure 2, has user-tunable bandwidth from 200 kHz to 56 MHz, and 12-bit A/D and D/A converters operating up to 61.44 MSPS, along with other features and the performance that are needed to build a signal chain spanning 70 MHz to 6 GHz. Critical operating parameters are user-adjustable “on the fly” for optimum matching to the application requirements. Using this component reduced the overall footprint of the entire analog front end (AFE) while keeping power consumption for this portion of the design in the 1 W region — essential to stay within the product power budget.

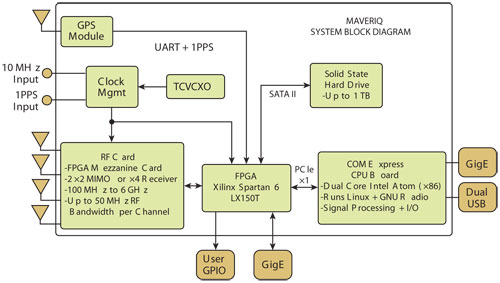

The overall Maveriq unit, shown in Figure 3, supports 2×2 MIMO or 4-channel receiver configurations via a pair of AD9361s, with an RF tuning range from 100 MHz to 6 GHz, 1 kHz step size, and 2 msec tuning time. It includes an integrated GPS receiver with 1 PPS performance, up to a 1 TB internal SSD supporting data recording 100+ MB/sec (sustained), and gigabit Ethernet for interfacing to external systems.

The processing function is centered on a dual-core Intel ×86 CPU running Linux plus an FPGA for signal-processing tasks, along with run-time loadable/executable software applications, all supported by an available software-development kit (SDK) for custom applications. The entire unit is 9.1" × 6.6" × 1.7" (23 × 16.7 × 4.3 cm), weighs 1.9 lbs (0.9 kg) and dissipates 15 W (depending on FPGA and I/O usage).

Of course, processing power is inadequate without suitable RF performance. The receiver has a typical noise figure of less than 8 dB and typical IIP3 of –10 dBm. Transmit-side performance parameters (such as bandwidth, tuning and speed) complement the receive side numbers, along with output power of +5 dBm.

Although the AD9361 IC was a key enabler for this design, additional improvements are always on the horizon. Certain applications require stretching the RF performance down to the 20 MHz range and below, which is beyond the reach of the AD9361. Further, selection of RF components such as low noise amplifiers (LNA) capable of operating down to 20 MHz can also be a challenge, especially for size and power constrained designs. It is simplistic to think that advances in low-power processing coupled with the availability of large amounts of memory plus high-speed digital I/O and connectivity — all driven by Moore’s law — are sufficient for a viable small, high-performance SDR. The reality is that the front end channel for both receive and transmit paths is just as important, and developments in RF ICs that combine analog processing, filtering and conversion not only minimize the algorithm burden, but make much of the actual SDR performance possible.

| 联系人: | 廖小姐 |

|---|---|

| 电话: | 010-57308810 |

| 传真: | 010-57308810 |

| Email: | info@ur-bj.com |

| 网址: | www.ur-bj.com |

| 地址: | 北京市通州区翠景北里21号 |